## Application Note

# Designing for Xilinx LCAs with FutureNet

# Section 1: Entering an LCA Design Using FutureNet

## **Contents**

| Before You Begin                                         | 2  |

|----------------------------------------------------------|----|

| Setting Up Your Schematic                                | 2  |

| Using Title Blocks                                       | 2  |

| Creating Multiple-Page Drawings                          | 3  |

| Creating an LCA Design Using FutureNet                   | 3  |

| FutureNet Attributes                                     | 3  |

| Creating Functional Blocks                               | 4  |

| Naming Signals and Buses                                 | 5  |

| LCA Naming Conventions                                   | 6  |

| Creating Symbols with MEMGEN                             | 7  |

| Using the Xilinx Library — Xilinx Primitives and Macros  | 8  |

| XC2000 Library Exceptions for Use with FutureNet         | 9  |

| XC3000 Library Exceptions for Use with FutureNet         | 4  |

| XC4000 Library Exceptions for Use with FutureNet         | 20 |

| Representing Power and Ground Signals                    | 20 |

| Representing IOBs                                        | 21 |

| Using Constraint Flags                                   | 23 |

| Controlling Block Placement — LOC= and LOC<> Constraints | 24 |

| Using XC3000 Drawings for XC4000 Designs                 | 28 |

| Using XC3000 Symbols on an XC4000 Drawing                | 28 |

| Exceptions to The XC3000 Symbol Conversion Process       | 29 |

This section includes information you need to enter an LCA design with FutureNet, and is divided according to the following categories.

- Before You Begin Information on setting up your schematic, using title blocks and creating multiple-page drawings.

- Creating an LCA Design Using FutureNet This section provides detailed information about creating functional blocks, using naming conventions, and adding various characteristics to your LCA design.

- Using Xilinx Primitives and Macros Xilinx primitives and macros are the building blocks of an LCA design. This section provides information to assist you in using these library elements to create an LCA design.

## Before You Begin

artist My

K. KOMETE SOME L

SIN THE

#### Setting Up Your Schematic

Before beginning your LCA design, you should be aware of two important aspects of FutureNet design hierarchy and documenting your design.

- Design Hierarchy Set up your design hierarchically, using functional block symbols to create a hierarchical design file.

- Documenting Your Design Set up your design in a manner that allows you to track

design revisions accurately and to create design documentation that is consistent in

appearance. FutureNet provides title block primitives to assist you in this process.

#### Using Title Blocks

11.7 - 11 in

Using title blocks allows you to select items such as the LCA part type, document, and design revisions. The title block primitives in the Xilinx library are listed in the following table.

| Market Market Control of the Control | Title Block | Size   | Dimension    | Border              |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--------|--------------|---------------------|--|

| 1 516 - 2017/16 - 1<br>40 - 13 - 13 - 13 - 13 - 13 - 13 - 13 - 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | TBLOCKA     | A      | 8-1/2 x 11   | Yes                 |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | TBLOCKB     | В      | 11 x 17      | Yes                 |  |

| 7/364                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | TBLOCKC     | C      | 17 x 22      | Yes                 |  |

| ac bas abo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |             | D      | 22 x 34      | Yes                 |  |

| 1 112 54641                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | TBLOCKCP    | C      | 17 x 22      | Yes                 |  |

| 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |             | D      | 22 x 34      | Yes                 |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | TBLOCK      | В      | 11 x 17      | No                  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | TITL        | Same a | s TBLOCKB (X | (C2000 family only) |  |

Each title block contains a default string (attribute 81) that you can edit to reflect the desired part type. This part type is passed on to the XACT implementation software.

Note: You can use the -P option on the PIN2XNF command line to override any part type text in the title block.

o ber simili

#### **Creating Multiple-Page Drawings**

The XMAKE Automatic Design Translator runs DCM correctly if multiple-page drawings are properly identified. Multiple pages must have the same filename with sequentially-numbered extensions (.D01, .D02) instead of the default DWG extension. For example, if your top-level schematic (TOP) contains three pages, name these drawings TOP.D01, TOP.D02, and TOP.D03. If a lower-level module called MYMAC consists of two pages, the symbol name (File (8)) should be MYMAC and the two MYMAC schematics should be named MYMAC.D01 and MYMAC.D02.

When processing the MYMAC logic, XMAKE recognizes from the .D01 and .D02 extensions that MYMAC is a multiple-page schematic. XMAKE then automatically runs DCM with the following command line.

Cmd:DCM MYMAC.D01 MYMAC.D02

The resulting DCM file is called MYMAC.DCM and contains the logic from both pages. XMAKE automatically merges the MYMAC logic into the TOP logic at a later step in the translation process.

## Creating an LCA Design Using FutureNet

#### **FutureNet Attributes**

#### FutureNet Attributes Allowed by PIN2XNF

The PIN2XNF program allows only a subset of the attributes provided by FutureNet. The following FutureNet attributes are used by PIN2XNF to translate a FutureNet design to an XNF file.

| #  | Attr. | Description                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|----|-------|-----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 0  | СОМ   | Assigns a comment, which is ignored by PII                                                                                  | Assigns a comment, which is ignored by PIN2XNF.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| 2  | LOC   | Assigns an instance name to a symbol. Althorequired, they must be unique if used.                                           | ough LOC (2) names are not                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| 3  | PART  | Defines a Xilinx primitive symbol. Do not c (3) attribute.                                                                  | reate text with the PART                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| 5  | SIG   | Assigns a signal name to a net. Used for bot signals.                                                                       | h individual nets and bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| 8  | FILE  | Assigns a filename to a functional block synmust carry one and only one FILE (8) name macros are named with an attribute 8. | - 2.25 N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| 21 | PINO  | Defines an output pin name.                                                                                                 | Y _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| 22 | PNBT  | Defines a bidirectional pin name.                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| 23 | PINI  | Defines an input pin name.                                                                                                  | M. In the grant of |  |

Note: FutureNet reserves attributes 80 through 99 for use by application programs, such as PIN2XNF.

| #  | Description                                                                                                                                                                                                    |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 80 | Assigns CLB locations to flip-flops and CLB primitives, and IOB locations to I/O pads and IOB primitives. For XC4000 devices, attribute 80 labels can be used in place of some LOC= (attribute 83) parameters. |

| 81 | Assigns LCA part type.                                                                                                                                                                                         |

| 82 | Defines configuration statements on CLB and IOB primitives.                                                                                                                                                    |

| 83 | Assigns special LCA options.                                                                                                                                                                                   |

#### Assigning Attributes

CONTRACTOR OF

netras i se Diwicus Each alphanumeric field in FutureNet is assigned an attribute, whether it's the default attribute, - or one that gives more information about the field. The easiest way to assign an attribute for an alphanumeric field is to assign the attribute before you begin typing.

There are two ways to assign attributes to alphanumeric fields:

- For existing fields, use 'CH A to change the attribute currently assigned to the field.

- For new fields, use 'A to set the attribute before typing the alphanumeric data. Then that attribute is automatically assigned to each new field.

To change the text of an alphanumeric field, place the mouse cursor on the text and use 'R or press [Esc] to enter the text editing mode.

#### **Creating Functional Blocks**

A hierarchical module in FutureNet is represented by a functional block symbol. A functional block can have any number of pins, each of which represents an input to or an output from the hierarchical module.

The functional block symbol itself is created by using the .F command. The format of this command is as follows.

F width height border\_width border\_height

The first two parameters, width and height, determine the dimensions of the block symbol itself. The last two parameters, border width and border height, specify the size of the border area around the symbol. The pins on the functional block are displayed in this border area.

To add pins to the functional block, use the following commands.

| ~    | 10 E    | 2   | •   |

|------|---------|-----|-----|

| 1 '0 | mma     | nnd | Ino |

| V.   | 1111116 | mu  |     |

| Entry | Function                               |

|-------|----------------------------------------|

| 94,   | Add regular pin stub.                  |

| .>    | Add clock pin stub.                    |

| O     | Add inverted (bubbled) pin stub.       |

| .>0   | Add inverted (bubbled) clock pin stub. |

| .D    | Delete pin stub.                       |

|       |                                        |

The different types of pin stubs are provided only as a graphical convenience. Each pin stub was a stable of the same meaning to the translation software.

10571320

douter to the second

#### Naming Functional Blocks

Once a functional block has been created, both the symbol itself and its associated pins must be named. Use the following conventions when assigning names to a functional block for an LCA design.

Each functional block must be identified by a single label which carries the FILE (8) attribute. This label represents the name of the functional block symbol, as well as the name of the underlying drawing. Therefore, the FILE (8) name must be a valid DOS filename of 8 characters or less. Do not specify an extension as part of the FILE (8) name, as the translation software uses this name with various extensions. A FILE (8) name must also be a legal LCA name: see "LCA Naming Conventions" below. Each functional block in an LCA design must carry one and only one FILE (8) name.

For example, if the FILE (8) label on a functional block is MUX, the lower-level drawing which describes this block must be called MUX.DWG. Similarly, the PIN2XNF translation program will expect to find a file called MUX.PIN, which is created from MUX.DWG as described later in this application note.

The name given to each pin on a functional block must be assigned one of three attributes: PINI (23) for input pins, PINO (21) for output pins, or PNBT (22) for bidirectional pins. Each pin name must match exactly the name of the corresponding signal on the lower-level drawing. See "Naming Signals and Buses" for more information on signal naming.

#### Using Functional Blocks for Multiple-page Drawings

A single functional block can be used to represent a module which is contained on more than one lower-level drawing page. In this case, the single FILE (8) name on the functional block represents the combined lower-level schematic, no matter how many drawing pages it contains.

If you intend to use the XMAKE program to translate your design, you must name each page of the lower-level schematic using the same base filename, with the extensions D01, D02, D03 and so on. The functional block for this schematic should carry one FILE (8) label, which matches the base filename of the lower-level drawings. Do not include an extension in the FILE (8) name. Drawing files named in this manner are recognized by XMAKE as multiple pages of a single schematic, and will be combined correctly.

For example, if a lower-level schematic consists of the drawings MUX.D01, MUX.D02 and MUX.D03, the FILE (8) label on the functional block would read "MUX."

For more information on XMAKE and the translation process, see section 1.

#### Naming Signals and Buses

Every signal in an LCA design, including both individual nets and buses, should be assigned a name. A name for either a net or a bus is assigned using an attribute SIG (5) label.

The only restriction on individual net names is that each must be a valid LCA name: see "LCA Naming Conventions" later in this section. If two nets on the same drawing carry an identical name, they will be considered connected by the translation software. Therefore, if nets are not intended to be connected, they must have unique names. Each distinct net must carry no more than one name. If a name is not assigned to a net, the translation software assigns an arbitrary unique name. Since these unique names are difficult to trace when debugging the design, it is highly recommended that you name every net.

Note: The name given to IOBs in the completed LCA file is based on the name of the net connected to the I/O pad. If you do not name this net, the resulting IOB does not carry a user name, and is only identified by the actual package pin designation.

Note: If a hierarchical module contains multiple pages (see "Using Functional Blocks for Multiple-page Drawings" earlier in this section), nets which have identical names are connected across page boundaries.

There are two steps to naming a bused signal:

- 1. Name the individual nets of the bus.

- 2. Name the bus itself to identify the component nets.

Each individual net in a bus is assigned a normal SIG (5) name, which must be a valid LCA name. Alternatively, an individual net may be assigned a positive integer value as a name, also carrying the SIG (5) attribute. Using consecutive integer values will make the name of the bus itself simpler, as shown below.

The name of the parent bus signal (or trunk) specifies the name of the bus itself, as well as the names of the individual nets. The parent bus name carrying the SIG (5) attribute is expressed in one of the following forms.

```

name<net1, net2, j:k, net3,...>

name[net1, net2, j:k, net3,...]

```

The name of the parent bus is represented by name. Any individual nets that are named with consecutive integer labels can be specified in the form j:k, where j and k are the bounds of the consecutive range. Individual nets that are not part of an integer range must be specified explicitly. These various net specifications must be separated by commas.

If a bus signal goes into a functional block using a bus pin stub, the individual net specifications for the upper-level bus signal must match exactly the individual net specifications for the bus signal on the lower-level drawing. Although the name of the bus pin must match the name of the lower-level bus signal, these names need not match the connecting upper-level bus signal. Every individual net on the upper-level bus does not have to be split out from the bus, but the translation software will issue a binding mismatch message to warn you of this condition.

As an example of bus naming, consider a bus consisting of ten individual signals. If eight of the component nets are labeled with the integers 0 through 7, and the remaining two nets are labeled A and B, the parent bus could be specified as IN<0:7, A, B>. When expanded by the translation software, the individual nets would be called IN<A>, IN<B>, IN<0>, IN<1>, IN<2> and so on.

#### **LCA Naming Conventions**

All names given to symbols and signals in an LCA design must be valid for the XACT Development System. The requirements for all LCA names are outlined below.

- User-defined LCA names may contain only the following characters:

A-Z a-z 0-9 \$ < >

- The characters < and > have special meaning in FutureNet and should only be used when defining bus signals.

• Names can be up to 1024 characters in length, although some translation programs may not preserve the entire name. Names must contain at least one non-numeric character, and can begin with any legal character. The case of alphabetic characters is ignored; uppercase and lowercase characters are considered identical.

#### Creating Symbols with MEMGEN

The Xilinx memory compiler, the MEMGEN program, creates RAM and ROM memories within Xilinx XC4000 LCAs. With MEMGEN, you can automatically create memories ranging from 1 to 32 bits wide and up to 256 words deep.

The MEMGEN program is described in the XACT Design Implementation User Guide. The example below illustrates how to use the MEMGEN program to create a memory symbol for the FutureNet schematic editor. For a full description of the memgen program, consult the Design Implementation User Guide.

To use the MEMGEN program, a description of the memory — including its type, size and contents — is placed in a Memory Definition File. In this example, MEMGEN creates the file. Run MEMGEN with the filename that is used for the memory.

```

memgen shifter

```

MEMGEN creates a Memory definition file called SHIFTER.MEM and an XNF file to represent it. To create a FutureNet symbol for this example memory function, enter the command:

```

memgen shifter -f

```

The Memory Definition File for shifter was created previously by MEMGEN. This command causes MEMGEN to read the SHIFTER.MEM definition file, from which it creates a FutureNet command file called SHIFTER.CMD. MEMGEN displays the following messages on the screen.

```

Reading your Memory Definition File called 'shifter.mem' ...

Creating a FutureNet(tm) symbol command file for the memory function

...

Symbol command file saved as 'shifter.cmd' ...

NOTE:

----

To automatically save the FutureNet memory symbol in your MEMGEN update

```

```

From the prompt, enter

'fn shifter.cmd'

Within the Xilinx Design Manager (XDM) select

'DesignEntry',

'Symbol'

```

library, do either of the following:

The command file created by MEMGEN can then be used to create the actual RAM symbol. To use the SHIFTER.CMD file, you would run FutureNet from the DOS prompt in the following manner.

fn shifter.cmd

This runs the FutureNet schematic editor, draws the memory symbol using the instructions in the SHIFTER.CMD command file, and saves it into a FutureNet update library named MEMGEN.SYM. The last instruction in the command file exits from the FutureNet program.

The command file created by MEMGEN always stores its symbol in the library MEMGEN.SYM, which it creates if it does not already exist. You can then use the symbol by specifying the MEMGEN symbol library in FutureNet in the following manner.

LIB MEMGEN.SYM

Then load the memory symbol using the load (.L) or load and tag (\*) command. Alternatively, the memory symbol can be created using the XACT Design Manager, using the Symbol function found under the FutureNet menu selection. When you select the Symbol option, the design manager will display all FutureNet command files (CMD file extension) found in the current directory. If you select one of these files, the Design Manager runs FutureNet, draws the symbol, saves it into the MEMGEN.sym update library, and then returns to the XDM screen.

## Using the Xilinx Library — Xilinx Primitives and Macros

As stated at the beginning of this section, the Xilinx library contains primitives and macros, which are the building blocks of any LCA design. Primitives are basic logic elements, such as gates and flip-flops. Macros are combinations of various primitives or other macros that are used to implement common functions. They are classified as either hard or soft macros.

This section provides information on using the Xilinx library to create an LCA design. This section also describes several Xilinx symbols that have a special usage in FutureNet.

**Note:** The functions of all Xilinx primitives and macros are explained in the Macro Library. FutureNet-specific information on certain symbols is described in this section.

#### The Xilinx Libraries

The Xilinx library for the FutureNet Schematic Editor consists of FutureNet logic symbols and macros for schematic entry of LCA designs. It also contains translator programs that translate a FutureNet drawing file (DWG) into the Xilinx Netlist Format file (XNF).

Note: Use only parts from the Xilinx library for creating LCA designs and user macros.

#### Loading Parts from the Xilinx Libraries

To load symbols from the Xilinx symbol library into your design, use the following FutureNet commands.

#### Note:

- Load & Tag (\*) The Load Symbol command loads the symbol at the graphics cursor location and initiates a tag and drag.

- Load (.L) This command works the same way as the \* command, except that tag and drag is not initiated.

Iction I'm

- Reflect (.RE) This command reflects a symbol about its horizontal or vertical axis, creating a mirror image of the symbol.

- Rotate (.R) The rotate command enables you to rotate the symbol in 90-degree

increments. In addition, the symbol is tagged so that it can be moved using the mouse or

arrow keys.

**Note:** Refer to the appropriate Macro Library for more detailed information regarding gate-naming conventions.

## XC2000 Library Exceptions for Use with FutureNet

#### The XC2000 Family CLB and IOB Primitive

#### **CLB Primitive**

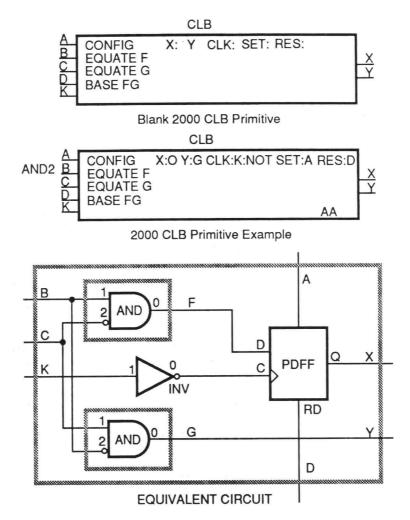

You can enter portions of a design's logic directly in terms of CLBs instead of entering the logic schematically. A CLB primitive allows you to directly specify CLB configurations. This permits precise control of logic partitioning. In addition, when using FutureNet you can only specify a CLB's FGM base configuration in a CLB primitive. The FGM BASE configuration is the same as the FG — two functions of up to three variables, but the two function outputs are multiplexed together and controlled by the B input.

Figure 1 contains the symbols for a blank CLB primitive, a configured CLB primitive, and the equivalent circuit. You must specify the BASE, CONFIG, EQUATE F, and EQUATE G commands for the CLB. These text strings in the symbol (attribute 82) are passed through PIN2XNF, XNFMAP, and MAP2LCA to XACT as configuration for the CLB. These commands are described in further detail later in this section.

| Command   | Description                                                            |  |

|-----------|------------------------------------------------------------------------|--|

| BASE      | Sets the CLB's base configuration (F, FG, or FGM).                     |  |

| CONFIG    | Specifies the CLB's internal interconnections.                         |  |

| EQUATE F= | Configures a CLB's logic F function.                                   |  |

| EQUATE G= | Configures a CLB's logic G function.                                   |  |

| m         | D. C.D. W. W. and W. aland the description of the CI. Diaming Clamping |  |

The CLB symbol has A, B, C, D, K, X, and Y pins that correspond to the CLB's pins. Signals connected to these pins in the schematic are connected to the corresponding CLB in the LCA design.

**Note:** The configuration commands must be consistent with the connections. For example, if you use the A input in an equation, then connect a signal to the A pin.

The CLB symbol contains a blank template for each of the required configuration text strings. Edit the strings to include the desired configuration commands using the -Esc key editing mode in FutureNet.

You must ensure that the configuration commands are correct. Neither PIN2XNF, XNFMAP, nor MAP2LCA checks them; they pass them to XACT. When XNFMAP reads the design file, it issues error messages if these commands contain errors. Also use the DRC command in XACT to detect errors in the CLB configuration.

You can specify (in the symbol) the location in which to place the CLB or IOB using an alphanumeric string with attribute 80: for example, the -AA string in Figure 1. The string must be a valid CLB name (for example, AA, AB and AC). If you do not specify a location, an arbitrary location is assigned. Then use APR or XACT to assign a suitable location.

Figure 1 XC2000 CLB Primitive and Example

Above is a symbol for a blank XC2000 CLB primitive, a configured CLB primitive, and the equivalent circuit. You must specify the BASE, CONFIG, EQUATE F, and EQUATE G commands for the CLB. CLB primitives allow you to directly specify CLB configurations. This permits precise control of logic partitioning.

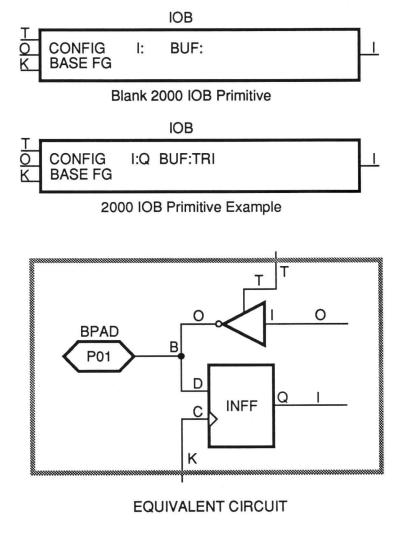

#### IOB Primitives

Figure 2 contains the symbols for a blank IOB primitive, a configured IOB primitive, and the equivalent circuit. You must specify the CONFIG and BASE commands for the IOB. These alpha strings in the symbol (attribute 82) are passed through PIN2XNF, XNFMAP, and MAP2LCA to XACT as configuration for the IOB. These commands are described in further detail later in this section.

| Command | Description                                    |

|---------|------------------------------------------------|

| BASE    | Sets the CLB's base configuration (I/O).       |

| CONFIG  | Specifies the CLB's internal interconnections. |

The CLB and IOB symbol contains a blank template for each of the required configuration text strings. Edit the strings to include the desired configuration commands using the Esc key editing mode in FutureNet.

You must ensure that the configuration commands are correct. Neither PIN2XNF, XNFMAP, nor MAP2LCA checks them; they pass configuration commands on to XACT. When XACT reads the design file, it issues error messages if these commands contain errors. Use the DRC command in XACT to detect errors in the block configuration.

You can specify the location (in the symbol) in which to place the IOB by using an alphanumeric string with attribute 80. The string must have a valid IOB pin (for example, P12 or A13). Refer to the datasheet pin assignments for the valid IOB pin names.

For a package type other than PGA, add a P in front of the pin number. For PGAs the pin name is as listed in the datasheet (for example, J11). To use an unbonded IOB, you must run editlea in XACT to find the unbonded pad name (for example, U74).

Note: IOB primitives allow you to directly specify IOB configurations.

Figure 2 IOB Primitive and Example

#### CLB and IOB Primitive Commands

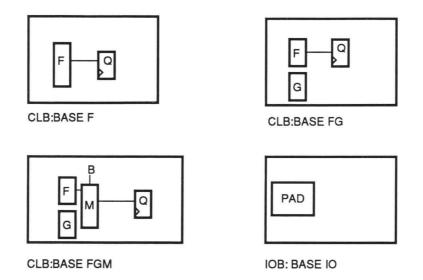

#### BASE [F/FG/FGM/IO]

This command sets the base configuration.

| Command               | Description                                                                                      |

|-----------------------|--------------------------------------------------------------------------------------------------|

| I/O                   | For IOBs only.                                                                                   |

| F                     | One function of up to four variables.                                                            |

| FG                    | Two functions up to three variables each.                                                        |

| FGM                   | Same as FG, but the two function outputs are multiplexed together and controlled by the B input. |

| and the second second |                                                                                                  |

See Figure 3 for an illustration of these XC2000 Family CLB and IOB base configurations.

Note: BASE F, FG and FGM are for CLBs; BASE IO is for IOBs.

Figure 3 XC2000 Family CLB and IOB CLB Primitives BASE Configurations

#### CONFIG tag: setting

This command specifies logic element inputs and the storage element function. For XC2000 Family Designs the config tags and settings are as follows:

| TAG  | BASE F   | BASE FG   | BASE FGM  |

|------|----------|-----------|-----------|

| X:   | F Q      | F G Q     | M Q       |

| Y:   | F Q      | FGQ       | M Q       |

| Q:   | FF LATCH | FF LATCH  | FF LATCH  |

| SET: | AF       | AF        | A M       |

| RES: | DF       | DG        | D M       |

| CLK: | KCFNOT   | K C G NOT | K C M NOT |

Note: For BASE FGM, M=F if B=1 and M=G if B=0.

TAG BASE I

I: PAD Q

BUF: ON TRI

EQUATE (Block): Configure a CLB's Logic Function(s)

[EQUATE] tag = Boolean expression

The symbols you can use in the Boolean expression are as follows.

| Symbol | Boolean Equivalent |  |

|--------|--------------------|--|

| ~      | NOT                |  |

| *      | AND                |  |

| @      | XOR                |  |

| +      | OR                 |  |

#### **XC2000 CLBMAP Primitive**

Use CLBMAP primitives to control the partitioning of logic into a CLB. Though a CLBMAP is not logic, you use it to change the mapping of logic. To use a CLBMAP primitive, first define a logic group on the schematic that fits into one CLB. Determine the input and output signals for this logic group and assign them to the appropriate pins on the CLBMAP as shown in Figure 4. You may leave some pins unconnected; however, you must specify all signals associated with the logic group on the CLBMAP.

The PUC text string (attribute 84) inside the CLBMAP primitive stands for Pins Unlocked and Closed. This means that CLBMAP pins can be swapped with other pins (unlocked), but no more additional logic can be added to the CLB (closed). PLC (Pins Locked and Closed) is the other option; this means that the CLBMAP pins are locked onto the specified CLB pins. You can use the P (Pinlock APR Constraint Flag) in conjunction with the PUC attribute to lock only the pins which have pinlock flags attached to them.

IPAD I AOIN I BUF O BO PXX

IPAD I BOIN I BUF O BO PXX

IPAD I AIIN I BUF O BI PXX

AND O SUM2 I OBUF OPAD O PXX

Figure 4 CLBMAP Primitive and Example

Note: CLBMAP primitives are used to control the partitioning of logic into a CLB.

## XC3000 Library Exceptions for Use with FutureNet

#### The XC3000 Family CLB and IOB Primitive

You can enter portions of a design's logic directly in terms of CLBs and IOBs instead of entering the logic schematically. CLB and IOB primitives allow you to directly specify CLB or IOB configurations. This permits precise control of logic partitioning. In addition, you can specify (in FutureNet only) the FGM configuration via the CLB primitive. The FGM BASE configuration is similar to the FG configuration: two functions of up to four variables, but the two function outputs are multiplexed together and controlled by the E input.

#### CLB Primitive

Figure 5 contains the symbols for a blank CLB primitive, a configured CLB primitive, and the equivalent circuit. You must specify the BASE, CONFIG, EQUATE F, and EQUATE G commands for the CLB. These alphanumeric strings in the symbol (attribute 82) are passed through PIN2XNF, XNFMAP, and MAP2LCA to XACT as configuration for the CLB. These commands are described in further detail later in this section.

| Command            | Description                                                |

|--------------------|------------------------------------------------------------|

| BASE               | Sets the CLB's base configuration (F, FG, or FGM).         |

| CONFIG             | Specifies the CLB's internal interconnections.             |

| EQUATE F=          | Configures a CLB's logic F function.                       |

| EQUATE G=          | Configures a CLB's logic G function.                       |

| The CLB symbol has | A B C D E DI EC K RD X and Y pins, which correspond to the |

The CLB symbol has A, B, C, D, E, DI, EC, K, RD, X, and Y pins, which correspond to the pins of the CLB; signals connected to these pins in the schematic are connected to the corresponding CLB in the LCA design.

Note: The configuration commands must be consistent with the connections. For example, if you use the A input in an equation, then a signal should be connected to the A pin.

You can specify (in the symbol) the LCA location of the CLB using a text string with attribute 80 (for example, the -AA string in Figure 1-5). The string must be a valid CLB name (for example, AA, AB or AC). If you do not specify a location, an arbitrary location is assigned. Then use APR or the XACT Design Editor to assign a suitable location.

**Note:** CLB primitives allow you to directly specify CLB configurations. This permits precise control of logic partitioning.

#### IOB Primitives

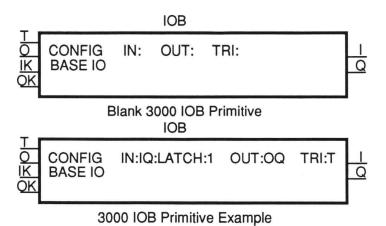

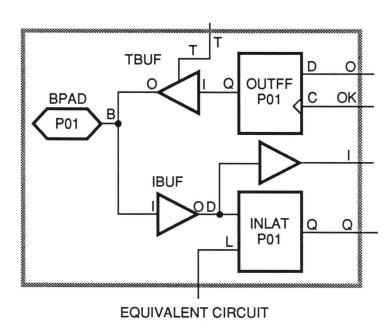

Figure 6 contains the symbol for a blank IOB primitive, a configured IOB primitive, and the equivalent circuit. You must specify the CONFIG and BASE commands for the IOB. These alphanumeric strings in the symbol (attribute 82) are passed through PIN2XNF, XNFMAP, and MAP2LCA to the LCA file as configuration for the IOB. These commands are described in further detail later in this section.

| Command | Description                                    |  |

|---------|------------------------------------------------|--|

| BASE    | Sets the CLB's base configuration (I/O).       |  |

| CONFIG  | Specifies the CLB's internal interconnections. |  |

The CLB and IOB symbols contain a blank template for each of the required configuration text strings. Edit the strings to include the desired configuration commands using the Esc key editing mode in FutureNet.

You must ensure that the configuration commands are correct. Neither PIN2XNF, XNFMAP, nor MAP2LCA checks them; they pass them to the LCA file. When editlca within XACT reads the design file, it issues error messages if these commands contain errors. Use the DRC command in XACT to detect errors in the CLB configuration.

Figure 5 XC3000 CLB Primitive and Example CONFIG X Y: DX: DY: CDK: DSTDR: ENCLK: EQUATE F **EQUATE G** BASE FG Blank 3000 CBL Primitive CLB CONFIG X:QX Y:QY DX:F DY:G CDK:K ENCLK:EC EQUATE F = A \* B \* E \* QY EQUATE G = QX \* A \* E \* QY BASE FG 3000 CBL Primitive Example EC **FDC** C CE **FDC** Q Y CE

You can specify (in the symbol) the IOB's location using a text string with attribute 80. The string must have a valid IOB pin (for example, P12 or A13). Refer to the datasheet pin

Note: For package types other than PGA, add a P to the front of the pin number. For PGAs the pin name is as listed in the datasheet. To use an unbonded IOB, use the unbonded pad name used by XACT (such as U74).

Note: IOB primitives allow you to directly specify IOB configurations.

assignments for the valid IOB pin names.

Figure 6 XC3000 IOB Primitive and Example

#### **CLB and IOB Primitive Commands**

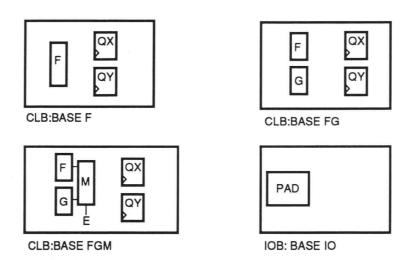

#### BASE [F/FG/FGM/IO]

BASE [F/FG/FGM/IO]

This command sets the base configuration.

| Command                                                                                 | Description                                                                                      |  |

|-----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|--|

| I/O                                                                                     | For IOBs only.                                                                                   |  |

| F                                                                                       | One function of up to five variables.                                                            |  |

| FG                                                                                      | Two functions up to four variables each.                                                         |  |

| FGM                                                                                     | Same as FG, but the two function outputs are multiplexed together and controlled by the B input. |  |

| See Figure 7 for an illustration of these XC3000 Family CLB and IOB base configurations |                                                                                                  |  |

Note: BASE F, FG and FGM are for CLBs; BASE IO is for IOBs.

Figure 7 XC3000 Family CLB and IOB Primitive BASE Configurations

## CONFIG tag: setting

#### CONFIG tag:setting

This command specifies logic element inputs and the storage element function. For XC3000 Family Designs the config tags and settings are as follows:

| TAG     | BASE F | BASE FG | BASE FGM |

|---------|--------|---------|----------|

| X:      | F QX   | F QX    | M QX     |

| Y:      | F QY   | G QY    | M QY     |

| DX:     | DI F   | DI F G  | DI M     |

| DY:     | DI F   | DI F G  | DI M     |

| CLK:    | K NOT  | K NOT   | K NOT    |

| RSTDIR: | RO     | RO      | RO       |

| ENCLK:  | EC     | EC      | EC       |

| TAG  | BASE I                     |

|------|----------------------------|

| IN:  | I IQ IKNOT FF LATCH PULLUP |

| OUT: | O OQ NOT OKNOT FAST        |

| TRI: | T NOT                      |

|      |                            |

**Note:** For BASE FGM, M=F if E=0 and M=G if E=1.

| TAG  | BASE I |  |

|------|--------|--|

| I:   | PAD Q  |  |

| BUF: | ON TRI |  |

#### EQUATE (Block): Configure a CLB's Logic Function(s)

[EQUATE] tag = Boolean expression

The symbols you can use in the Boolean expression are as follows.

| Symbol | Boolean Equivalent |  |

|--------|--------------------|--|

| ~      | NOT                |  |

| *      | AND                |  |

| @      | XOR                |  |

| +      | OR                 |  |

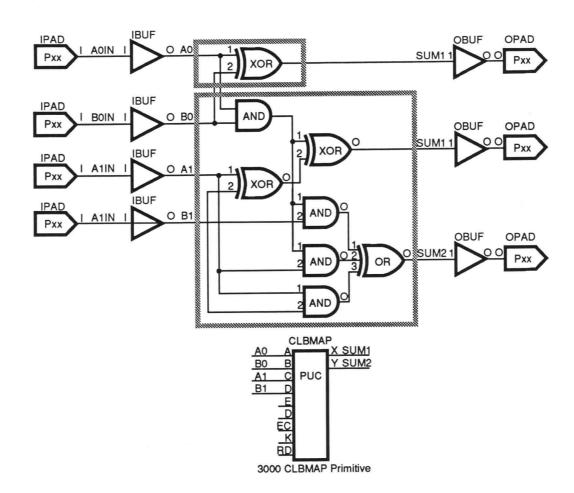

#### XC3000 CLBMAP Primitive

Use CLBMAP primitives to control the partitioning of logic into a CLB. Though the CLBMAP is not logic, you can use it to change the mapping of logic. To use a CLBMAP primitive, first define a logic group on the schematic that fits into one CLB. Determine the input and output signals for this logic group and assign them to the appropriate pins on the CLBMAP as shown in Figure 8. You can leave some pins unconnected; however, you must specify (on the CLBMAP) all signals associated with the logic group.

The PUC text string (attribute 84) inside the CLBMAP primitive stands for Pins Unlocked and Closed; this means that the CLBMAP pins can be swapped with other pins (unlocked) and no more additional logic can be added to the CLB (closed). The other option is PLC (Pins Locked and Closed), meaning that the CLBMAP pins are locked onto the specified CLB pins. You can use the P (Pinlock APR Constraint Flag) in conjunction with the PUC attribute to lock only the pins that have an attached pinlock flag.

Note: Use CLBMAP primitives to control the partitioning of logic into a CLB.

Figure 8 CLBMAP Primitive and Example

# XC4000 Library Exceptions for Use with FutureNet

#### Representing Power and Ground Signals

#### VCC Logical High

The VCC symbol flag is used to tie a net to a logical HIGH state. Load the VCC flag (symbol name: VCC) and attach it to the desired net, using a junction dot if a T connection is formed. The actual VCC symbol appears as +5 on the schematic. A net tied to VCC cannot have any other source.

When the PPR program encounters a net tied to the VCC flag, it removes any logic that is disabled by the VCC signal. Note that a VCC signal will only be physically implemented in the LCA if the logic it sources is not removed by PPR.

Alternatively, a net may be tied to VCC by giving it the name VCC, using a standard SIG (5) attribute. Any net with the name VCC will be treated exactly as a net tied to a VCC flag.

#### GND Ground

The GND symbol flag is used to tie a net to a logical LOW state. Load the GND flag (symbol name: GND) and attach it to the desired net, using a junction dot if a T connection is formed. A net tied to GND cannot have any other source.

When the PPR program encounters a net tied to the GND flag, it removes any logic that is disabled by the ground signal. Note that a GND signal will only be physically implemented in the LCA if the logic it sources is not removed by PPR.

Alternatively, a net may be tied to ground by giving it the name GND, using a standard SIG (5) attribute. Any net with the name GND will be treated exactly as a net tied to a GND flag.

#### **Representing IOBs**

#### PAD External LCA Pad

The PAD primitive represents one of the external pads on the LCA that are electrically connected to the metal leads on the device package. Use this primitive to indicate a connection to an external pin. The PAD primitive must be connected to either an I/O buffer (such as IBUF or OBUF) or an I/O storage element (such as INLAT or OUTFF). The PAD has no directionality and should be used for LCA input signals, output signals, or bidirectional signals.